## **DESIGNING A LOW-POWER LNA FOR PORTABLE EEG ACQUISITION APPLICATIONS**

**Tula sumanya** PG Scholar, Department of Electronics and Communication Engineering, CMR Institute of Technology, Hyderabad, Telangana(Affiliated to JNTU Hyderabad and Accredited by NBA New Delhi)

**Dr.T.Santosh Kumar** Associate professor, Department of Electronics and Communication Engineering, CMR Institute of Technology, Hyderabad, Telangana.(Affiliated to JNTU Hyderabad and Accredited by NBA New Delhi)

### **Abstract:**

In this project we propose a low-power low-noise amplifier (LNA) that can be used wideband operations while providing simultaneous input matching and output load. A component sharing technique and a component-Q-aware impedance-matching technique are introduced in the proposed LNA circuit. The proposed LNA, implemented in a 45nm CMOS process, can operate in a wideband mode 2.4 GHz. The expected voltage gain LNA is 20dB. The expected LNA power consumes less than 1mW of power from the 1V supply.

### **Introduction**

A circuit with a low-power low-commotion enhancer and a Gm-C super low-power channel is proposed in this paper for versatile electroencephalogram (EEG) procurement applications. The proposed circuit contains a two-stage chopper-balanced out completely reusing collapsed cascode (TSRFC) speaker and a second-request nonstop time Gm-C low elapse channel (LPF) with super low-power utilization. The clamor and information offset are diminished utilizing the chopper-balanced out strategy. A two-stage amplifier that comprises of composite semiconductors and a reusing structure is proposed for the amplifier. Contrasted with a common collapsed overflow CMOS amplifier, the proposed plan has higher DC gain and slew rate as well as lower input-alluded commotion. This circuit has a movable second-request Gm-C LPF with exceptionally low power utilization. The amplifier accomplishes a midband gain of 70 dB and a  $\square$ 3dB data transfer capacity in the reach 0.1-212 Hz.

Also, the amplifier is planned in 0.18- $\mu$ m CMOS process and the chip region of the proposed circuit with cushions is 450\_450 \_m<sup>2</sup>. The flexible LPF has a 100 Hz cut-off recurrence. The proposed circuit has an information alluded commotion of 0.7 Vrms, (0.1 \_ 100Hz) and a power utilization of 380 nW at 1 V s gadgets like electroencephalogram (EEG) gadgets have become versatile and remote. These little and compact gadgets can screen patients' medical issue in-home or anyplace in a clinic. Given the prerequisites for versatility and solidness, clinical checking instruments should be more modest, lighter, and power-productive with diminished clamor and offset. These prerequisites alongside the requirement for higher recognition exactness are viewed as in planning these versatile instruments. An EEG signal is extremely frail with a sufficiency going from 20 to 200 V. The EEG recurrence goes from 0.1 to 100 Hz, to be specific in the accompanying groups: delta (, 1\_4Hz), theta (, 4\_8Hz), alpha (, 8\_12Hz), beta (, 12\_30Hz), and gamma (30\_50Hz) [Besides, the skin-terminal connection point makes a huge

DC offset voltage which can be in the request for \_300 mV. These two difficulties can upset the fundamental sign and lessen the identification precision. The requirement for exact obtaining and enhancement, alongside requiring low-power low-plentifulness EEG signals, makes it exceptionally testing to plan a low-commotion speaker and channel for EEG gadgets. Clamor and offset decrease techniques ought to be utilized in this cycle while limiting power utilization. The tiny proportion of sign to-clamor of mind cues that we attempt to notice, the wide assortment of commotion sources are the greatest difficulties in utilizing EEG gadgets. Due to the low-recurrence scope of EEG flags, the ruling circuit clamors shift from the warm commotion to 1/f and popcorn clamor. At the contribution of intensification part of numerous EEG or electrocardiogram (ECG)

circuits, the slashing strategy has been applied to change over DC input signals into AC flags that can then be capacitively coupled to the information phase of a capacitively coupled intensifier. Balance and 1/f clamor are upmodulated away from DC by cleaving strategy, so high accuracy, microvolt offset and low 1/f commotion can be accomplished. These attributes make such enhancers extremely advantageous for the intensification of little low-recurrence signals. While cleaving is applied to a functional speaker, info signal is first moved to the odd music of the recurrence lastly moved back to DC. In the interim, the offset and 1/f clamor of the enhancer are up regulated by the chopper modulator at the result of the speaker to the odd sounds of the slashing recurrence. Accordingly, preferably, an offset and 1/f commotion free operation amp is gotten

The fundamental trans conductance enhancer as EEG instrumentation speaker (IA) in a large portion of past works is the collapsed cascode speaker and the more normal sound decrease strategy in bio potential low-clamor speakers (LNAs) is chopper adjustment. Chopper adjustment is a fundamental technique for relieving 1/f commotion. A few geographies that successfully utilize chopper adjustment for low-power bio potential detecting have as of late been created Chopper adjustment is acknowledged through regulation and demodulation procedures that require a bunch of CMOS switches. Aside from limiting low-recurrence clamors, these switches acquaint commotions with the readout interface circuit and add to the all-out input-alluded clamor figure. It is demonstrated that by including a half-sized source-channel shorted switch (sham switch), it is feasible to fundamentally lessen the charge infusion and dynamic offset commotions during entryway voltage change drop to nothing.

### 1.1 Review of beneficiary designs

The reason for the recipient in remote correspondence framework is to play out specific activities expected for the got sign like enhancement, recurrence interpretation, and simple to digital transformation with sufficient sign to-clamor proportion before exposed to advanced signal handling. The exhibition of a collector is dissected by the capacity to get serious areas of strength for the frail sign within the sight areas of strength for of. The presentation measures are communicated with regards to responsiveness, selectivity, loyalty, and dynamic reach. The choice of recipient design depends on execution, cost, and power dispersal. The reconciliation level alongside the quantity of off-chip parts decides the expense of the beneficiary. The current collector geographies in RF handsets are Zero-IF, Heterodyne, Low-IF, and Wideband IF. The depiction of these beneficiary models is momentarily given in this proposal.

### 1.2 Direct transformation recipient

An immediate transformation recipient (DCR) is likewise named as homodyne, synchrodyne, or zero-IF beneficiary. It was created in 1932 by a group of British researchers. This collector gives the most normal answer for identify data sent by a transporter in a solitary transformation stage. The worked-on block chart of a commonplace direct change collector is displayed in Fig.A synchro dyne beneficiary is a radio recipient that demodulates the approaching radio transmission utilizing a coordinated discovery driven by a nearby oscillator. The sign transformation (RF to IF) to baseband is finished in a solitary recurrence change. The RF signal from the radio wire is pre-sifted by a band pass channel (BPF) to smother the transmissions out of the gathering band. The sign is enhanced at the low-clamor speaker (LNA) stage and down-changed over into zero middle recurrence (IF) by the blender stage. The subsequent IF signal recurrence is the distinction between the RF and nearby oscillator signal frequencies. On account of the stage and recurrence regulated signals, the down-transformation cycle ought to be acted in quadrature to forestall signal sidebands from associating on each other. As the neighborhood oscillator is focused in the ideal channel, it requires sign and commotion to possess both the upper and lower sidebands. The down transformation design delivers a picture at nothing IF recurrence, and consequently no picture channel is required significant quality of the immediate transformation collector is that enhancement and sifting are for the most part performed at the baseband instead of at the RF. The necessary sign is chosen with the assistance of a low-pass-type baseband channel (BBF). The low-pass channel with a data transfer capacity of a

portion of the image rate eliminates the bordering channels at baseband. As the separating is performed at low frequencies, channels can be acknowledged in on-chip without utilizing outside high-Q parts. Most of the sign handling activity happens at low frequencies, in this manner limiting power utilization. The DCR kills the picture dismissal issue existing in other radio structures [2]. In any case, a lacking adequacy and stage balance between in-stage and quadrature-stage signs can build the piece blunder rate [3, 4]. It has its own hindrances, for example, an exceptionally delicate to gleam clamor and DC counterbalances. These issues can be dispensed with in the wideband framework configuration by utilizing high-pass channels. The DCR evades the intricacy of the very heterodynes at least two recurrence changes, IF stages, and picture dismissal issues. Ongoing examination works demonstrated that the zero-IF is consistently well known and is generally utilized for RF applications because of its effortlessness, less off-chip parts, and limited power. The majority of the recipients utilize a similar RF front-end which incorporates LNA, blender, and an oscillator. joining level, less off-chip parts, and power dispersal. The depicted front-end circuits are undeniably focused on for direct transformation beneficiaries.

CMOS is dependably modest in handling cost and one of the most outstanding advancements for the execution of simple plan with no transformations. Further, it can furnish better combination of computerized hardware with superior execution simple circuits. Additionally, it gives the chance of complete framework on-chip, whole simple front-end, and the advanced demodulator carried out on a similar kick the bucket. CMOS innovation has the capacity to work at a lower supply voltage than the BiCMOS innovation. This is because of the way that every semiconductor has a common switch on voltage of 0.7-0.8 V, and subsequently the base stock voltage expected for BJT circuits is around 2-3 V. Yet, current CMOS processes give various limit voltages ( $V_t$ ) like high, moderate, and low norms. For example, MOS semiconductors with a lower limit can be used in simple or computerized circuits, where speed is significant. Then again, gadgets with a higher edge are valuable when the low-power utilization of the computerized circuits is impacted by spillage flows. This component empowers the hardware configuration under low working voltage in any event, when innovation is downsized toward profound submicron CMOS processes. Innovation scaling is the essential calculate accomplishing elite execution circuit plans and frameworks. Every decrease in CMOS innovation scaling has a diminished entryway delay, multiplied the gadget thickness, and a decreased energy for each change.

### Writing

As the interest of portable correspondence, high information rate correspondence, and the client limit is consistently expanding step by step. Accordingly, to meet the necessities, third era of remote correspondence was presented by Europe, America and Japan overall and was known as 3G. As opposed to 1G framework, 3G chiefly centered around information correspondence. It carried the office to utilize web on the portable handset with fast and high limit. Presently the interest of high velocity correspondence is further expanding and to have significantly quicker information rate and other high-level administrations for portable clients, the cutting edge is sent off for example 4G. Presently for future prerequisites, scientists are likewise dealing with LTE principles. Remote correspondence isn't just zeroing in on voice transmission at far off area, different administrations of remote systems administration are likewise helpful for supporters. For instance, Wi-Fi (Wireless Fidelity), Wi-Max (Worldwide Interoperability for Microwave Access) and remote sensor networks [1-5].

Throughout the entire existence of remote correspondence, data security, transfer speed necessity and heartiness are the leftover significant elements. Wideband and UWB enjoys benefit of communicating signal with fast with least contortion. This multitude of stuffs have been examined for UWB radars from traditional tight band radars. The elements shown are of age, radiation and handling of UWB radar signals, evoked by change of sign waveform during the time spent area, by appearance of the shared reliance between signal waveform and radio wire directivity and others [6-10].

As UWB enjoys various benefits in all suitable band in term of speed, these remote advances, consistently request a transmitter recipient engineering which give adequate circuit level increase low NF and high linearity with LP utilization. These transmitter collector structures might contrast for various application. Thusly, it becomes critical to concentrate on all the determination of transmitter beneficiary design for a specific band of recurrence as Wi-Fi, Wi-Max and different remote sensor networks [11-13]. IEEE

802.15.4 is another standard that tends to the need of low-rate remote individual region organizations (LR-WPAN) with an emphasis on empowering unavoidable remote sensor networks for private, business and modern applications. The standard is portrayed by keeping an elevated degree of straightforwardness, considering minimal expense and low power executions. A short, specialized presentation of the IEEE 802.15.4 norm and dissects its relevance for building computerization applications has been examined [14-16].

A prologue to handset plan for second and third plan determination is constantly expected for age of remote correspondences frameworks from the end client. Different handset front-end related experiment details and their connection to explicit handset qualities are made sense of. A survey of a few collector structures and their reasonableness for the two unique frameworks pursued by a viewpoint of future directions in handset front-end plan [17-18]. The primary normalization stage detail for impending third age (3G) remote interchanges is reaching a conclusion. As is commonplace for normalization work, adequate simple execution has been expected and prevalent accentuation has been put on balance and coding. Nonetheless, late updates to the normalization report for the European wideband CDMA (W-CDMA) proposition, empower an expectation of required execution for the RF front end. Such necessities are significant in planning business items for the new market. In this article, collector necessities for the portable unit are determined as far as perceived by the RF plan [19-20].

CMOS Technology is a suitable choice to plan RFIC circuit. Subsequently, it become essential to sum up the innovation compromise between all boundaries for execution of RF incorporated circuits for remote interchanges. Radio handset circuits have an exceptionally expansive scope of necessities including NF, linearity, gain, stage clamor, and power scattering. The benefits and hindrances of every one of the contending advances Si, CMOS and bipolar intersection semiconductors (Bjt's), Si/SiGe HBT's and GaAs Misfit's, PHEMTS and HBT's will be analyzed of these necessities. As the low power is dependably popular for RFIC circuit so it becomes vital to a tradeoff between existing geography with CMOS innovation [21-25].

The extension of the market for convenient remote specialized gadgets has given a colossal push to the improvement of another age of low-power RFIC items. In this quickly developing climate where time-to-showcase limitations force tight timetables, having a decent plan technique, imaginative PC helped plan (CAD) devices, and a very much coordinated plan framework are key variables to progress. Thusly, depicting a plan framework created to give the creator all things needed to foresee the way of behaving of RFIC gadgets, including design and bundle parasitic impacts precisely. A ton of significance of an obvious and coordinated framework is for assembling a plan that meets particulars at the base expense, in the base time. A nearby connection between schematic, models, and design is of vital significance to guarantee the precision required for low-power RF plan [26-30]. Different plan difficulties on LP and LV have been examined and a front-end part of collector is manufactured, which consumes a ultra LP, size of sub-Mw [31]. A biasing metric is utilized to enhance the power dispersal in RF circuit in UWB application. In any case, as door and channel voltage is decreased, The MOS semiconductor went into subthreshold district with positive decrease in power utilization however it has a shudder effect in debasement in various boundaries, for example, productivity, gain and NF consequently a compromise expected to execute beneficiary engineering [32-]

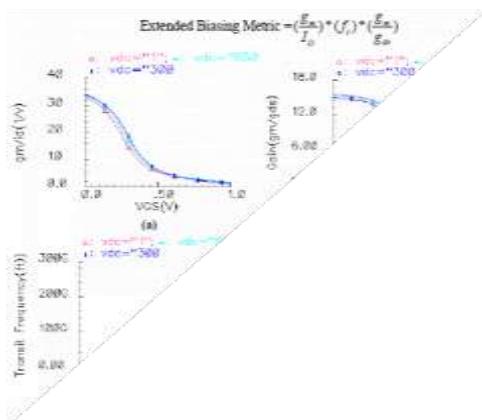

Figure. (a) Efficiency (gm/ID) v/s VGS. (b) Intrinsic gain (gm/gds) v/s VGS. (c) Transit frequency(ft) v/s VGS (d) Extended Biasing Metric v/s VGS

An extended biasing metric as shown in Figure 2.1(d) for different values of  $V_{GS}$ =0.3V, 0.65V, 1V, an optimized biasing point can be obtained in moderate inversion (MI) region for lower value of  $V_{GS}$ . The optimized point shifts toward the left side with decreasing value of this point towards decrement value of  $V_{GS}$ .

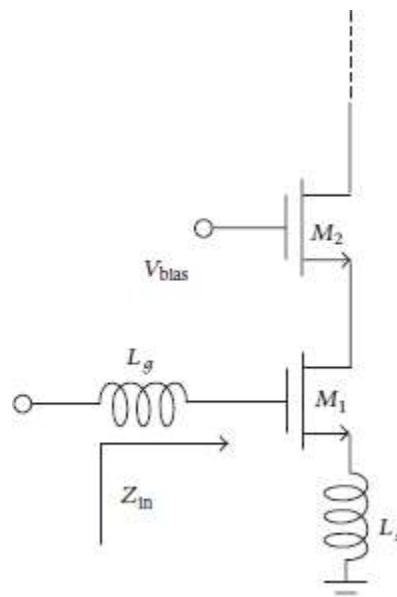

### 2.2.2 LNA Design using Source Degeneration

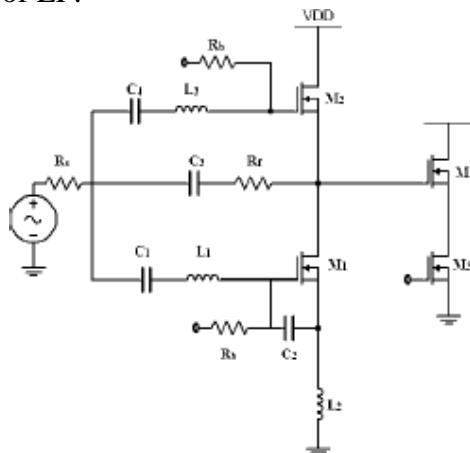

The proposed LNA using source degeneration technique is shown in Figure 2.2 in which transistor M1 connected in cascode with transistor M2. The voltage gain becomes large because in this technique gain is the multiplication of individual one. Signal is fed at gate terminal of the CMOS transistor to achieve the target of LP.

Figure. Schematic of LNA using Source Degeneration

Figure. Schematic of CCG-CS LNA

Second stage has an inductive coupling framed with inductors L1 and L2. Aside from coupling, this stage likewise gives a way to flag current. This mix is likewise used to reinforces the sign current. To

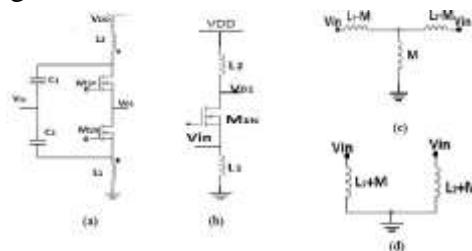

accomplish broadband information coordinating, the significance of these directors turns out to be very critical. These inductors reverberate with MOS capacitance C1, C2 and with inward parasitic capacitance and assume a significant part in guaranteeing that the information impedance is resistive. Figure 3.2(a) address the CCG phase of proposed circuit. Numerical comparable circuit of CG stage is displayed in Figure 3.2(b). Signal is taken care of to the two terminals of commonly coupled loop (essential (L1) and auxiliary (L2)). These loops structure a numerically identical circuit of a T-curl as displayed in Figure 3.2(c). Inductance presented by these curls are L1+M and L2+M (displayed in Figure 3.2(d)), where M is considered as shared coupling among inductance and given by . In the primary stage these coupling inductor are utilized to diminish the region and power. Next resulting phase of CCG stage is commonly coupled CS having the dynamic and detached part as L3. C3, M2N and commonly coupled loop L4 and L5. Primary reason for CS stage is to accomplish the objective of decreased commotion at high recurrence with level addition in the ideal band.

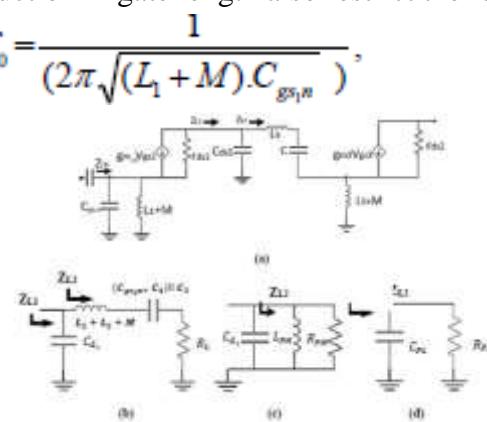

Figure 3.2 First stage configuration (a) CCG stage (b) CG equivalent to CCG stage (c) T-Coil equivalent of mutually inductors (d) Uncoupled two coil inductor

### 3.2.1. Input Impedance of Proposed LNA

Figure 3.3(a) represents the equivalent circuit of the proposed LNA. The input impedance at the source terminal is defined as:

$$Z_{in} = \left( \frac{1}{g_{m1n}} + \frac{Z_{L1}}{g_{m1n} r_{ds1n}} \right) \left| \frac{1}{sC_{gs1n}} \right| s(L_1 + M)$$

where  $cgs1$ ,  $gm1n$  and  $r_{ds1n}$  are the internal gate to source parasitic capacitance, transconductance and drain to source resistance of transistor M1N, respectively. If the load impedance  $ZL1$  represented by Equation (3.2) is zero then it is a parallel combination of capacitor, resistor and inductor. Impedance behave just like a pure  $n$  ds  $r$   $1$  in  $Z$  resistance at frequency

If loading effect across the input matching is not considered, it will limit the bandwidth of the circuit. Reduction in gate length also restrict the loading effect of next stage.

Figure 3.3 Equivalent circuit (a) Proposed LNA (b) ZL2 and ZL1 (c) ZL2 equivalent at high frequency (d) ZL2 equivalent at low frequency

Planning Steps for Dimension of Devices

The schematic of proposed LNA as displayed in Figure

3.1 has three MOS semiconductor and uninvolved parts. Target particular are set as power dispersal under 1 mW, Voltage gain more prominent than 20dB, NF under 2dB and data transfer capacity of

12 GHz. Perspective proportion of the multitude of semiconductors have been determined with the particular of force dispersal and Voltage gain. While everything others detached parts esteem is determined utilizing transfer speed and NF. Planning step for perspective proportion of every semiconductor are as per the following.

- Ascertain the benefit of biasing current utilizing the biasing voltage and power dissemination.

- Set the worth of channel obstruction show that all semiconductors stay in immersions.

- Estimation of current in person's stages.

- Track down the worth of channel to source voltage of every semiconductor.

- Ascertain the worth of every transconductance from DC gain.

- Work out the worth of viewpoint proportion with the assistance of transconductance condition expected in immersion area.

### **. Proposed framework**

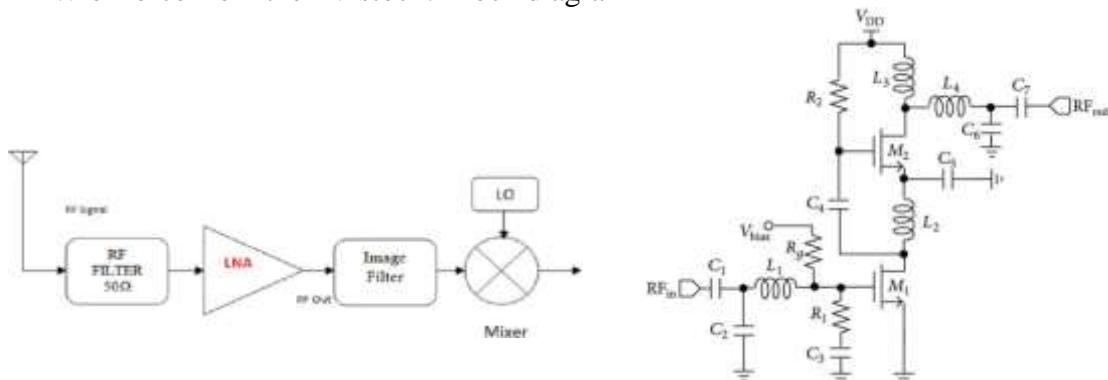

In this undertaking we propose a low-power low-clamor speaker (LNA) that can be utilized wideband tasks while giving concurrent information coordinating and yield load. A part sharing strategy and a part Q-mindful impedance-matching procedure are presented in the proposed LNA circuit. The proposed LNA, carried out in a 45nm CMOS process, can work in a wideband mode 2.4 GHz. The normal voltage gain LNA is 20dB. The normal LNA power consumes ~1mW of force from the 1V stock. Block diagram

Proposed LNA schematic

The above figure shows the proposed low power UWB LNA schematic. The ongoing sharing cascode speaker furnishes low-power attributes with low voltage supply. Note that  $M_2$  is the normal door phase of the cascode setup, which dispenses with the Miller impact and gives better segregation from the result bring signal back. The uninvolved parts  $C_1$ ,  $C_2$ ,  $C_3$ ,  $R_1$ , and  $L_1$  are embraced for the matching organization at the contribution to resound over the whole recurrence band. The resistors  $R_2$  and  $R_g$  are utilized to give predisposition voltage to the semiconductors  $M_1$  and  $M_2$ . The capacitor  $C_4$  gives signal coupling between the two phases. The capacitor  $C_5$  sidesteps the air conditioner current to the ground and tries not to couple to the principal stage. This influences gain evenness; thusly, it is feasible to give an ideal ac ground, yet gain levelness isn't impacted in the plan.  $L_2$  is the inductor heap of the main stage. The result matching organization is made of  $L_3$ ,  $L_4$ ,  $C_6$ , and  $C_7$ . In the cascode stages, the primary stage's clamor figure commitment is more than the subsequent stages. The primary stage's semiconductor size and inclination point ought to be streamlined for the low NF. The second stage's semiconductor size and inclination point ought to be enhanced for high linearity. The cascode LNA configuration is loaded with compromises between ideal addition, low commotion figure, info and result coordinating, linearity, and power utilization.

### **Low power Technique**

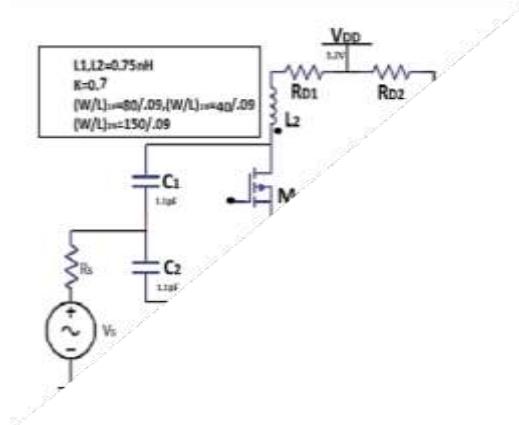

Figure below shows the basic cascode LNA. The current-reused configuration can be considered as two common-source amplifiers ( $M_1$  and  $M_2$ ). The current shared cascode amplifier provides a low-power characteristic under the low voltage supply. Because

$M_1$  and  $M_2$  share the same bias current, the total power consumption is minimized.

Cascode low noise amplifier

## RESULTS

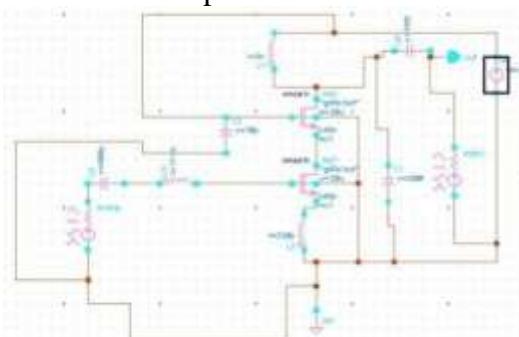

The LNAs have been simulated in 45nm CMOS technology. Furthermore, performance comparison of above-mentioned configuration has been depicted.

Fig: Schematic of the Proposed LNA

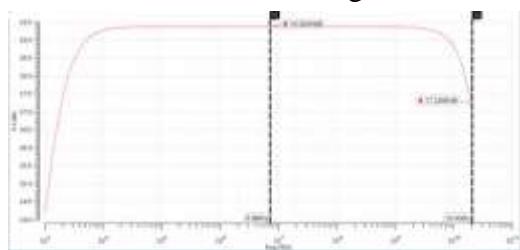

Fig: Gain of the Cascode LNA

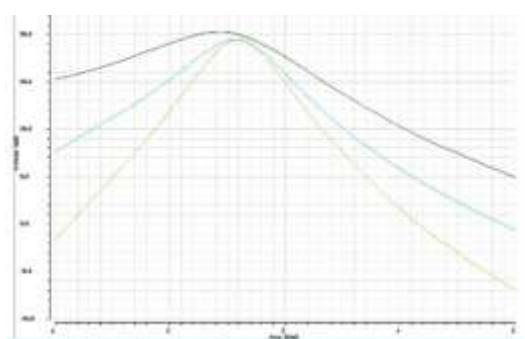

Fig: Power Gain, Transducer Gain, Available Gain of LNA

**Comparison Table:**

| <b>Parameters</b> | <b>With low power technique</b> | <b>This work</b> |

|-------------------|---------------------------------|------------------|

| Gain              | 11.94dB                         | 19 dB            |

| Band Width        | 3.1-6.5GHz                      | 3.1- 12.2GHz     |

| Noise Figure      | 0.202dB                         | 0.303dB          |

| Power Dissipation | 0.8mW                           | 0.62mW           |

| Technology        | 90nm                            | 45nm             |

## CONCLUSION

A low-power LNA is implemented and characterized in the 45-nm CMOS technology. Wideband and multiple narrowband impedance matchings are implemented together by sharing components and employing the *Q*-factor-aware design while consuming 0.62 mW in wideband mode and from 1-V supply voltage. The proposed LNA makes it a suitable candidate for CR application for the WSN.

## REFERENCES

- [1] Forty, Nicolas, et al. "Comparative analysis of new high data rate wireless communication technologies" from Wi-Fi to WiMAX", Joint International Conference on Autonomic and Autonomous Systems and International Conference on Networking and Services-(icas-isns' 05). IEEE, 2005.

- [2] Hamalainen, M., et al. "On the performance comparison of different UWB data modulation schemes in AWGN channel in the presence of jamming", Proceedings RAWCON 2002. 2002 IEEE Radio and Wireless Conference (Cat. No. 02EX573). IEEE, 2002.

- [3] R. S. Baker, "Marconi's achievement: Telegraphing across the ocean without wires", McClure's Magazine, pp. 291–299, Feb. 1902

- [4] R.W.Burns, Ed., Communications: An International History of Formative Years. The Institution of Electrical Engineers, 2004.

- [5] J. M. Cattell, "How the zeppelin raiders are guided by radio signals," Popular Science Monthly, pp. 632– 634, Apr. 1918.

- [6] Immoreev, Igor I., and PGS Dmitry V. Fedotov. "Ultra-wideband radar systems: advantages and disadvantages." IEEE Conference on Ultra-Wideband Systems and Technologies (IEEE Cat. No. 02EX580). IEEE, 2002.

- [7] Immoreev, I. "Use of Ultra-Wideband Location in Air Defence." Questions of Special Radio Electronics. Radiolocation Engineering Series 22, pp. 76-83, 1991.

- [8] Immoreev, I. "Ultra-wideband location: Main features and differences from common radiolocation." Electromagnetic Waves and Electronic Systems 2.1, pp. 81-88, 1997.

- [9] Immoreev, I. "Main features of UWB radars and differences from common narrowband radars." book "Ultra-wideband Radar Technology". Edited Taylor, JD; CRC Press, Boca Raton, London, New York, Washington, 2000.

- [10] Immoreev, Igor J., and Wu Shunjun. "Use ultra-wideband radar systems for increase information about target." 2001 CIE International Conference on Radar Proceedings (Cat No. 01TH8559). IEEE, 2001.

- Zou, Zhuo, et al. "A low-power and flexible energy detection IR-UWB receiver for RFID and wireless sensor networks." IEEE Transactions on Circuits and Systems I: Regular Papers 58.7, pp. 1470-1482, 2011